张任远

- 联系方式:rzhang@ynu.edu.cn

- 地址:信息学院2104号室

云南大学信息学院教授,日本奈良先端科学技术大学院大学客座教授,IEEE高级会员。从事超大规模集成电路设计与验证、智能计算芯片、人工智能硬件化、近似计算技术等方向教学与科研。

2003.9-2007.7 同济大学信息工程学院 电气工程及其自动化专业就读 (工学学士)

2008.4-2010.3 日本早稻田大学信息生产系统学院 集成电路系统专业就读 (工学硕士)

2010.4-2013.3 日本东京大学工学院 电子工程专业就读 (工学博士)

2013.4-2017.3 日本北陆先端科学技术大学院大学信息学院 助理教授

2017.4-2021.3 日本奈良先端科学技术大学院大学信息学院 助理教授

2018.10-2022.3 日本文部科学省学术振兴机构 客座研究员

2021.4-2024.3 日本奈良先端科学技术大学院大学信息学院 副教授

2024.4至今 日本奈良先端科学技术大学院大学信息学院 客座教授

2024.7至今 云南大学信息学院 教授

[Google Scholar] https://scholar.google.co.jp/citations?user=f8UqgYIAAAAJ&hl=ja

[DBLP] https://dblp.org/pid/73/9430.html

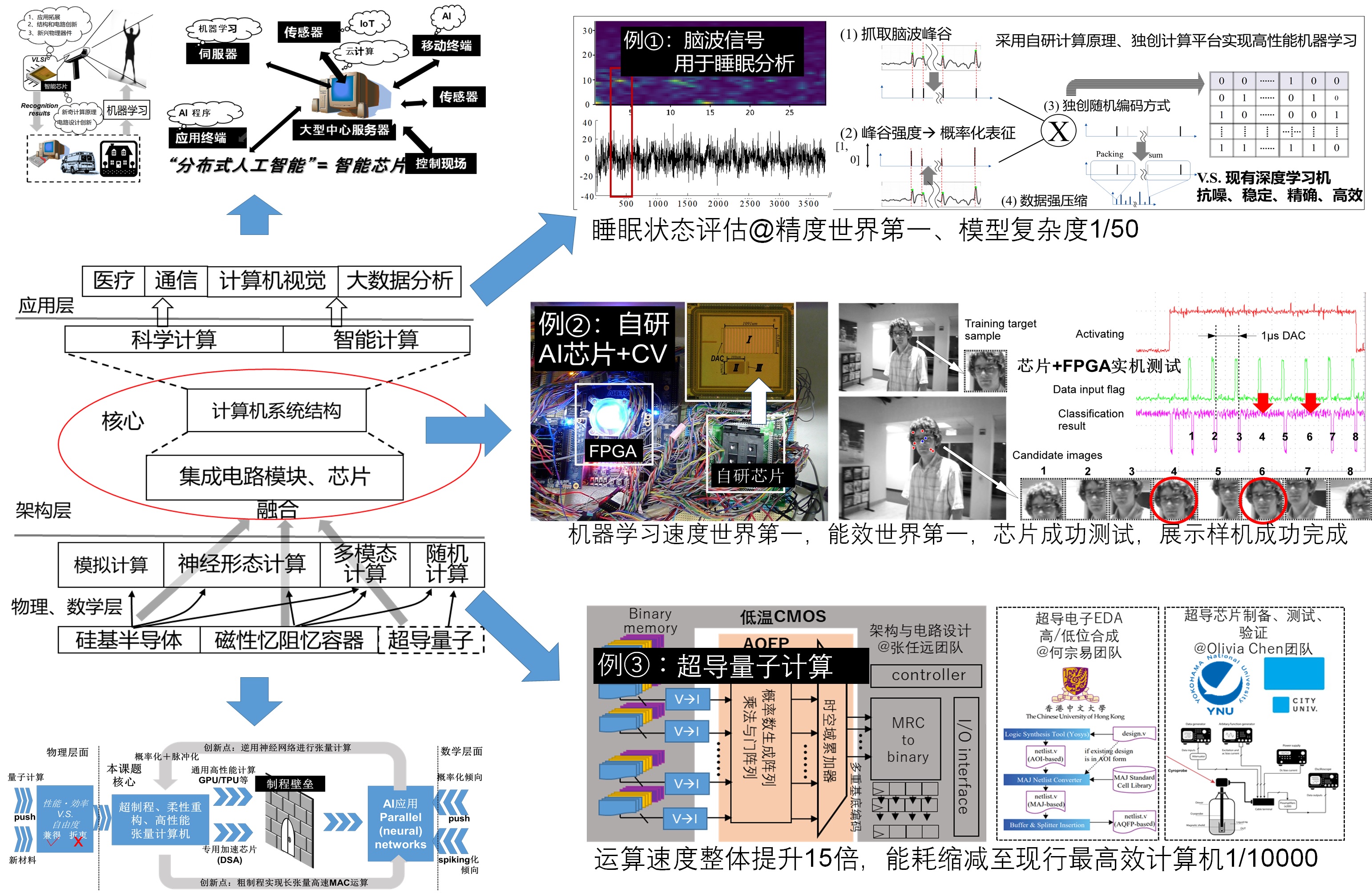

研究总体框架:如下图所示,涵盖智能计算芯片设计的应用级、系统级、结构级、电路级、器件级等多个层级。通过计算原理创新、软硬件协同设计、电路设计优化等手段力争实现1000TOPS/W的智能计算能效。主要技术核心是近似计算技术。

各辐射领域相关论文如下。

医疗数据分析:

[Med-1] Zheng Chen, Lingwei Zhu , Ziwei Yang, and Renyuan Zhang,“Multi-Tier Platform for Cognizing Massive Electroencephalogram“,International Joint Conference on Artificial Intelligence (IJCAI), main track, pp. 2464-2470.

[Med-2] Haohui Jia, Ziwei Yang, Pei Gao, Man Wu, Chen Li, Yirong Kan, and Renyuan Zhang, "Automatic Sleep Staging via Frequency-Wise Spiking Neural Networks," 2022 IEEE International Conference on Bioinformatics and Biomedicine (BIBM), Las Vegas, NV, USA, 2022, pp. 1028-1033.

[Med-3] Ren Imamura, Zhu Guangxian, Sang Duong Thi, Hoai Luan Pham, Renyuan Zhang, and Yasuhiko Nakashima: "Energy-efficient 3D Convolution using Interposed Memory Accelerator eXtension 2 for Medical Image Processing", MICAD'23, Dec. (2023)

片上机器学习:

[MLchip-1] R. Zhang, M. Kaneko, and T. Shibata, “An analog VLSI implementation of one-class support vector machine for multiclass classification of highly dimensional vectors,” Jpn. J. Appl. Phys., vol. 53,no. 4. pp. 04EE03. (2014)

[MLchip-3] R. Zhang, and M. Kaneko, “Robust and Low-Power Digitally-Programmable-Delay-Element Designs Employing Neuron-MOS Mechanism”, ACM Tran. Des. Autom. Electron. Syst. (TODAES), Vol. 20, No. 4, Article 64, (19 pages), September 2015.

[MLchip-3] R. Zhang, N. Uetake, T. Nakada and Y. Nakashima: "Design of Programmable Analog Calculation Unit by Implementing Support Vector Regression for Approximate Computing", IEEE MICRO, vol. 38, no. 6, pp.73-82, Dec. (2018)

超导量子计算:

[Quantum-1] O. Chen, Y. Wang, R. Zhang and N. Yoshikawa, "Design and Implementation of Stochastic Neural Networks Using Superconductor Quantum-Flux-Parametron Devices," 2022 IEEE 35th International System-on-Chip Conference (SOCC), Belfast, United Kingdom, 2022, pp. 1-6.

[Quantum-2] O. Chen, R. Zhang, W. Luo, Y. Wang and N. Yoshikawa, "Extremely Energy-Efficient Non-Linear Function Approximation Framework Using Stochastic Superconductor Devices," in IEEE Transactions on Emerging Topics in Computing (TETC), 2023.

[Quantum-3] Guangxian Zhu, Yirong Kan, Renyuan Zhang, Yasuhiko Nakashima, Wenhui Luo, Naoki Takeuchi, Nobuyuki Yoshikawa, Olivia Chen, “SuperSIM: A comprehensive benchmarking framework for neural networks using superconductor josephson devices”, Superconductor Science and Technology, 37(9), 2024.

计算机体系结构(粗粒度可重构阵列):

[CGRA-1] Jun Iwamoto, Yuma Kikutani, Renyuan Zhang and Yasuhiko Nakashima: "Daisy-chained Systolic Array and Reconfigurable Memory Space for Narrow Memory Bandwidth", IEICE Trans., Vol.E103-D, No.03, pp.578-589, Mar. (2020)

[CGRA-2] Tomoya Akabe, Hidenari Inamasu, Renyuan Zhang and Yasuhiko Nakashima: "Fusion of Multiple Core and Just-in-Time Compilable CGRA", IEEE Symposium on Low-Power and High-Speed Chips 2022 (poster), Apr. (2022)

[CGRA-3] Tomoya Akabe, Renyuan Zhang and Yasuhiko Nakashima: "Sensitivity Analysis of Memory Bandwidth on Column-Superposed Versatile Linear CGRA", IEEE Interregional NEWCAS Conference, Jun. (2023)

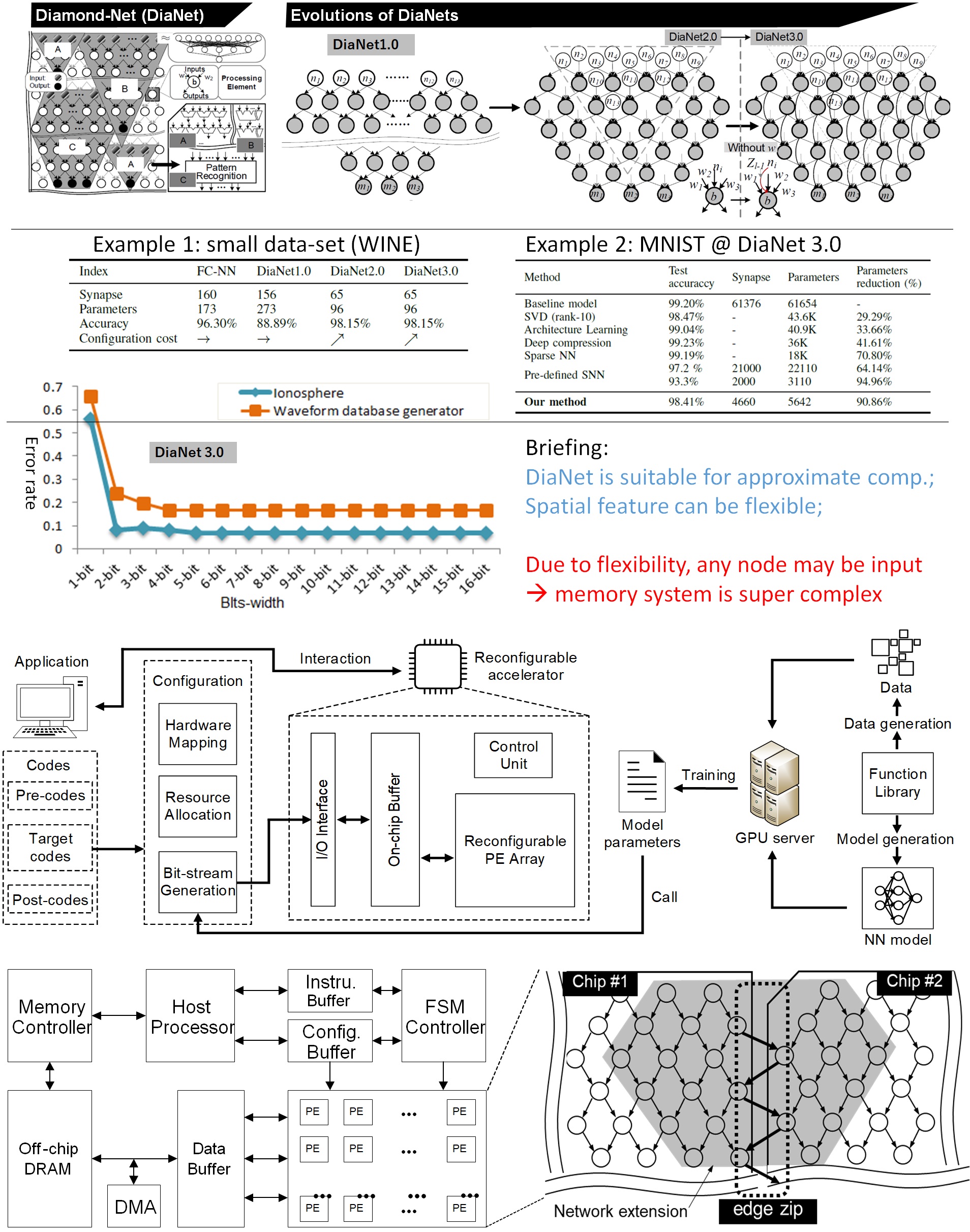

核心研究课题-1:空间可重构的近似计算技术在神经网络硬件化中的应用。如下图所示,本课题的技术起源是张任远2019年首创的一种二分叉式神经网络拓扑结构,命名为“钻石网络(DiaNet)”。区别于传统的全连接型神经网络(无论剪枝与否),DiaNet的任意一个Neuron只接受上层的两个输出Synapse并只通过另两个Synapse输出结果至次一层。由于每个Neuron+Synapse处理单元的连接数和功能极其简单并只发生局部互联,在芯片上可全并行地大量集成处理单元。经数学验证,这一阵列可自由切割为任意小块实现和传统全连接网络等效的功能。这个区块会体现出深而稀疏的拓扑特性和形如钻石的几何形态,故命名为钻石网络。目前全球并不存在全并行、大规模、可重构的神经网络架构,即便存在某种程度上的并行网络如TrueNorth、Loihi等,重构切割造成的冗余由于全连接属性也非常巨大。显然,DiaNet的重构和切割甚至多片互联几乎不会产生冗余。它的优势在于,一旦完成前期搭建,使用过程可以任意重构形态制成全并行处理器并几乎不产生资源冗余。这些区块大概分为三类:A类适用于少量操作数的非线性运算;B类实现向量的非线性运算;C类完整且全并行地映射移植一个复杂的神经网络用于模式识别。以MNIST为例,最新一代DiaNet实现MNIST的synapse数量仅为2000以下;加之所有运算均为2或3操作数运算,整体运算量在5000次单ALU操作等效换算以下。MNIST识别精度以98%的已知最优值为前提,DiaNet的运算开销相较于任意一种拓扑结构都达到了20倍以上的压缩。科学价值主要在于DiaNet对神经网络拓扑结构的通用全面优化。在算法研究领域,DiaNet的应用可缩减90%以上的全连接层synapse使用量,从而大量削减参数量并为算法创新提供新视野和可能性。在硬件实现研究领域,完全避免了长向量计算,提供了全并行可重构、芯粒(chiplet)、超低开销神经形态加速核等可能性。

[DiaNet-1] Renyuan Zhang, Yan Chen, Takashi Nakada, and Y. Nakashima: "DiaNet: An Efficient Multi-Grained Re-configurable Neural Network in Silicon", IEEE International System-on-Chip Conf.(SOCC), Sep. (2019)

[DiaNet-2] Y. Kan, M. Wu, R. Zhang and Y. Nakashima: "MuGRA: A Scalable Multi-Grained Reconfigurable Accelerator Powered by Elastic Neural Network", IEEE Transactions on Circuits and Systems I: Regular Papers, Jul. (2021)

[DiaNet-3] Chen Yan, Zhang Renyuan, Kan Yirong, Yang Sa, Yasuhiko Nakashima: "Bisection Neural Network Toward Reconfigurable Hardware Implementation", IEEE Transactions on Neural Networks and Learning Systems (TNNLS), Sep. (2022)

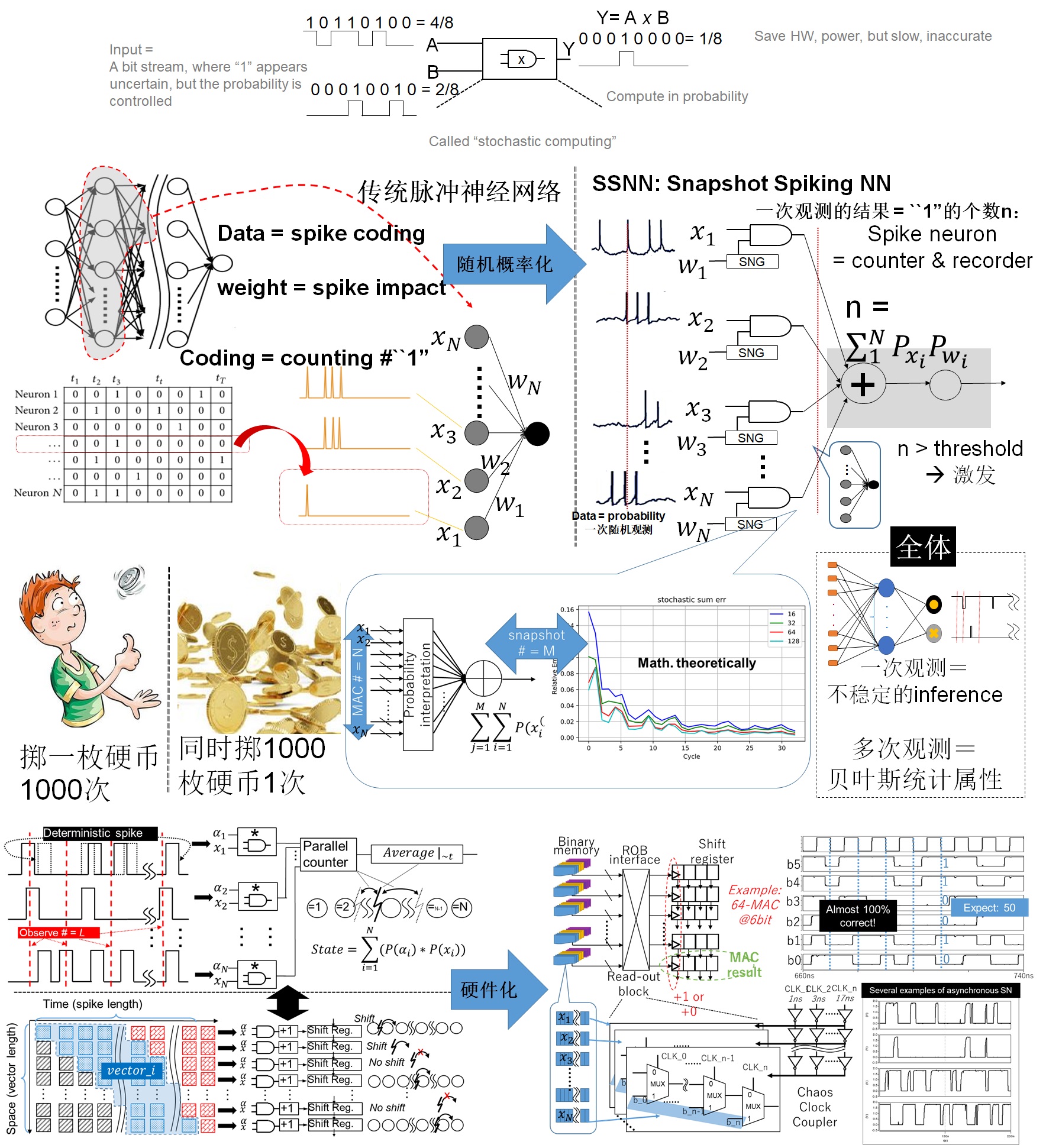

核心研究课题-2:时间可重构的近似计算技术在智能计算芯片研发中的应用。本课题的核心是如下图所示的随机计算原理及其硬件优化。该技术的目标是开发张量计算单元(Tensor Calculate Unit: TCU),基本原理受启发于多重伯努利实验中的概率理论常识和随机计算原理。

(a) 概率理论常识:对于一个概率表征对象的多次随机观测所得的累积观测值,与多个概率表征对象的一次观测所得的总和观测值具有互换性。从概率计算的角度分析,当观测次数越多或者对象的数量越大,计算的稳定性和精确度就越高。图中的预备试验显示了长加法运算的操作数、观测次数、精度间的关系。

(b) 随机计算原理:在随机计算(Stochastic Computing:SC)理论中,如果把对象操作数用一串随机生成但是概率可控(概率=操作数的值)的二元脉冲序列表示,任意两个随机串的“逻辑与”操作结果就是其所表示的两个操作数的乘法结果。加法则通过多路选通器实现。作为优势之一,这一技术被广泛认为可以大幅削减计算电路的开销。但很显然,计算精度严重依赖于随机串的长度,从而严重拖慢计算速度。操作数的增加将呈线性地加剧速度劣化。

上述两项产生了本质上的矛盾。本方向的核心研究课题是解决上述矛盾并使运算速度、硬件开销、可重构性、计算精度等各技术指标全面提升。

[SC-1] Renyuan Zhang, Tati Erlina, Tinh Van Nguyen, and Yasuhiko Nakashima: "Hybrid Stochastic Computing Circuits in Continuous Statistics Domain", IEEE Int. System-on-Chip Conf., pp.225-230, Sep. 8th-11th, (2020)

[SC-2] Tati Erlina, Renyuan Zhang and Yasuhiko Nakashima: "A Feasibility Study of Multi-Domain Stochastic Computing Circuit", IEICE Trans., Vol.E104-C, No.5, pp.153-163, May. (2021)

[SC-3] Guangxian Zhu, Yirong Kan, Renyuan Zhang and Yasuhiko Nakashima: "An Ultra-Compact Calculation Unit with Temporal-Spatial Re-configurability", IEEE Interregional NEWCAS Conference, Jun. (2023)